# ASPOCOMP Heart of your technology

Guideline for Laser Via reliability May 2021

## Guideline for Stacked 3- and 4-level Laser Via Design for Reliability

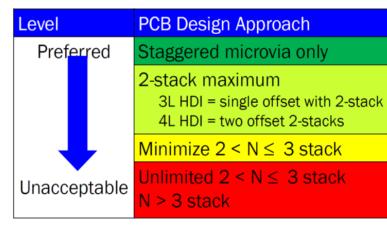

Design Guideline by IPC Task Group to mitigate reflow crack risk:

Courtesy - Motorola

#### Source IPC

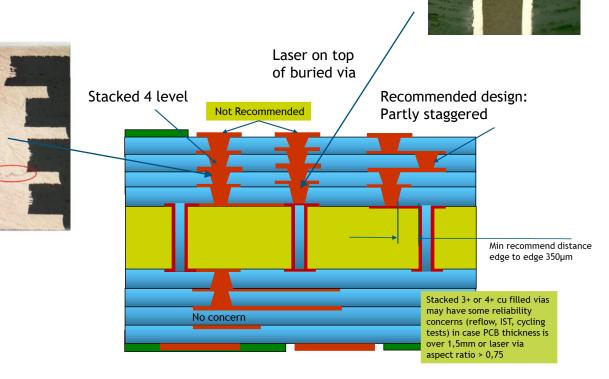

Thick HDI dielectric layers appears to be riskier, recommend <90u/layer and keep the AR  $\leq$  0,75 (see page 7)

Large and thick PCBs with 3-4 stacks looks like most concern

## IPC Links&comments about Stacked Microvia Reliability

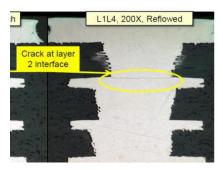

Stacked microvias can fracture at the metallurgical interfaces during reflow and thermal cycling

Product level failure unpredictable

Historical industry standard test methods are <u>not</u> effective in detecting failures due to intermittent conductivity.

IPC TM-650 2.6.27A technique duplicates assembly reflow and detects potential problems. However, IPC TM-650 2.6.26 is most widely used test method today.

Failures can be minimized by PCB design approach

Root cause(s) remains unknown; Industry in containment mode

IPC V-TSL-MVIA team formed and operating to identify root cause(s) and determine appropriate corrective actions. Team

<sup>19</sup> NOT working product acceptance issue

https://www.youtube.com/watch?v=aUa7ehIJ7fc

smt007-sept2020 magazine page 114 →

https://youtu.be/qtQRfNApkiE?t=1502

### "Weak Interface"/Stacked Microvia Reliability Denny Fritz, IPC Hall of Fame Member "IPC V-TSL-MVIA" Team